主營產品

新聞資訊

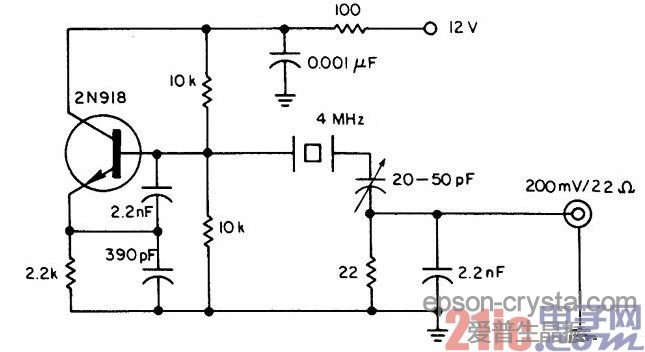

低噪音晶振電路設計指南

下面是一個愛普生晶體振蕩器電路圖,該振蕩器的輸出具有高光譜純度,并且很穩定。晶體管除了決定振蕩器的頻率,還可用作一個不期望諧波的低通濾波器,和邊帶噪音的帶通濾波器。噪音帶寬限制在低于100Hz。所有更高的諧波實際上為4MHz的基本振蕩頻率的第三諧波抑制60dB。石英晶體振蕩器是信號源的核心所在。在構建各種電子設備及通信系統設備等過程中,石英晶體振蕩器周圍的電路結構及設計對系統能否較大程度發揮功能起著重要的作用。特別是石英晶體振蕩器周圍電路,由于將在搭載數字電路的基板上以較高速度開關工作,較易產生噪音,所以設計電路之際必須對此十分注意。作為降低噪音電路設計的指南,本文將就使使用石英晶體振蕩器的周圍電路設計中的噪音對策進行解說。

選型與應用

-

2025-09-05EPSON晶體振蕩器(SPXO)在光模塊中的應用/選型推薦

-

2025-09-04EPSON寬溫實時時鐘模塊RX4901CE的優勢特點

-

2025-09-01愛普生RTC實時時鐘模塊解析與選型指南-愛普生戰略核心

-

2025-08-27愛普生VG5032EDN壓控晶振:為5G小基站提供高精度時鐘解

-

2025-08-21愛普生高精度IMU M-G570PR:多傳感器融合技術賦能工業級

-

2025-08-18愛普生SG-8018CA寬頻高精度可編程晶振,重塑工業與消費

466009906

466009906